### Understanding native event semantics

#### 9<sup>th</sup> JLESC Workshop

Anthony Danalis, Heike Jagode, Daniel Barry, Jack Dongarra

Knoxville, TN Apr 16th, 2019

# Performance API (PAPI): Overview

http://icl.cs.utk.edu/papi/

Latest PAPI Version 5.7

#### **PAPI**

- Library that provides a **consistent interface** (and methodology) for hardware performance counters, found across the system:

- i. e., CPUs, GPUs, on-/off-chip Memory, Interconnects, I/O system, File System, Energy/Power, etc.

- PAPI enables software engineers to see, in near real time, the **relation** between **SW performance** and **HW events across the entire compute system**

#### **PAPI**

- Library that provides a **consistent interface** (and methodology) for hardware performance counters, found across the system:

- i. e., CPUs, GPUs, on-/off-chip Memory, Interconnects, I/O system, File System, Energy/Power, etc.

- PAPI enables software engineers to see, in near real time, the relation between

SW performance and HW events across the entire compute system

#### **SUPPORTED ARCHITECTURES:**

AMD

- IBM Blue Gene Series

- IBM Power Series

- Intel Westmere, Sandy|Ivy Bridge, Haswell, <u>Broadwell</u>, <u>Skylake</u>, KNC, <u>Knights Landing</u>

#### **PAPI**

- Library that provides a **consistent interface** (and methodology) for hardware performance counters, found across the system:

- i. e., CPUs, GPUs, on-/off-chip Memory, Interconnects, I/O system, File System, Energy/Power, etc.

- PAPI enables software engineers to see, in near real time, the relation between SW performance and HW events across the entire compute system

#### SUPPORTED ARCHITECTURES:

- AMD

- ARM Cortex A8, A9, A15, ARM64

- CRAY: Gemini and Aries interconnects, power

- IBM Blue Gene Series, Q: 5D-Torus, I/O system, EMON power/energy

- **IBM Power Series**

- Intel Westmere, Sandy Ivy Bridge, Haswell, **Broadwell**, **Skylake**, KNC, **Knights Landing**

- Intel KNC, Knights Landing power/energy

- Intel RAPL (power/energy); power capping

- **InfiniBand**

- Lustre FS

- NVIDIA Tesla, Kepler: CUDA support for multiple GPUs; PC Sampling

- NVIDIA NVML

- Virtual Environments: VMware, KVM

### **Motivating Problem**

Hardware has become some complex that developers do not understand what it does and how it does it.

#### As a result it is not obvious:

- What to optimize

- How to optimize it

- How to measure the problem

Sometimes it's hard to tell what all this information means.

# Is it really that hard?

How many instructions does my program execute?

INSTRUCTIONS\_EXECUTED

# Is it really that hard?

How many instructions does my program execute?

INSTRUCTIONS\_EXECUTED

INSTRUCTION\_RETIRED

BR\_INST\_EXEC

BR\_INST\_RETIRED

How many L2 misses does my kernel cause?

LLC\_REFERENCES - L2\_RQSTS:CODE\_RD\_MISS

# Is it really that hard?

How many instructions does my program execute?

INSTRUCTIONS\_EXECUTED

INSTRUCTION\_RETIRED

BR\_INST\_EXEC

**Includes speculative execution**

BR\_INST\_RETIRED

**Executed and committed to state**

How many L2 misses does my kernel cause?

LLC\_REFERENCES - L2\_RQSTS:CODE\_RD\_MISS

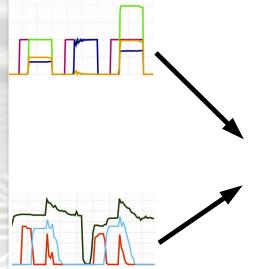

# Generating event signatures

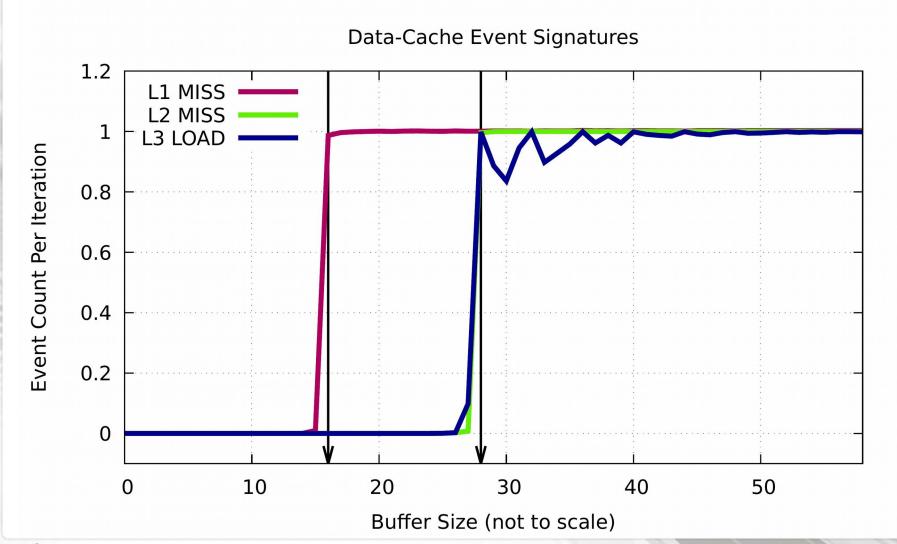

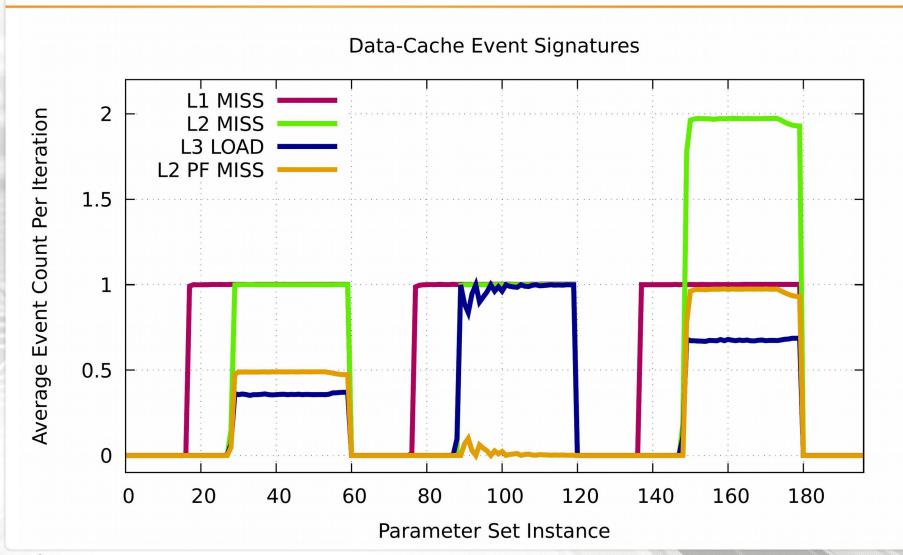

# Data-cache event signatures

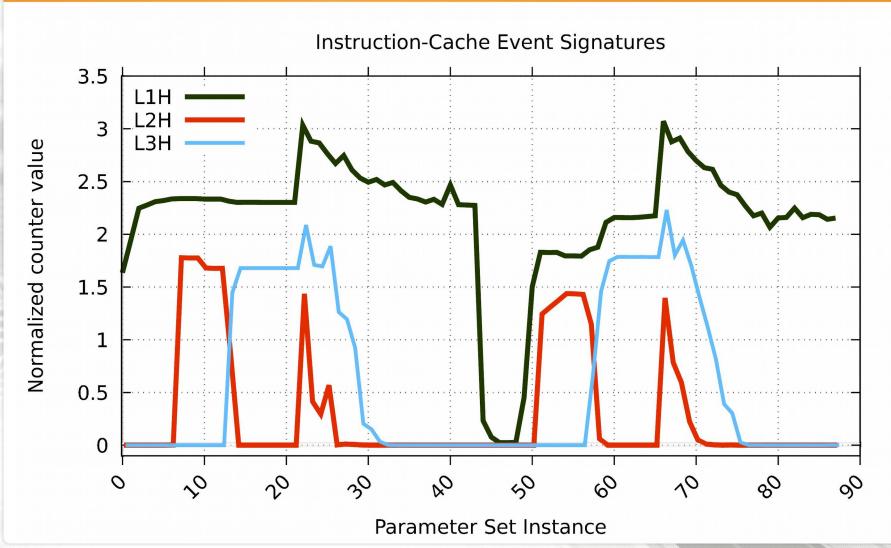

### Instruction-cache event signatures

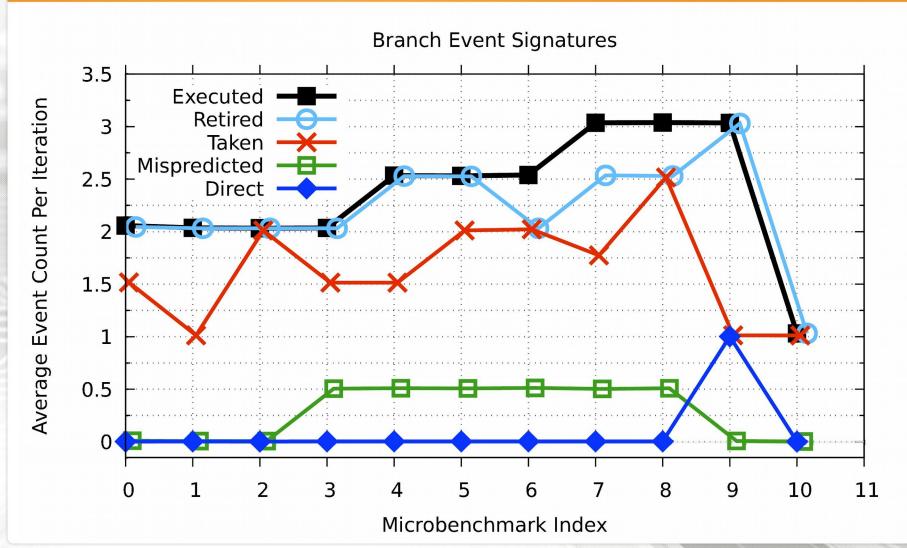

# Branch event signatures

### **Data Analytics**

$$\frac{1}{N} \sum_{i} \frac{(P_i - M_i)^2}{\overline{P} \cdot \overline{M}}, \quad \overline{P} = \frac{1}{N} \sum_{i} P_i, \quad \overline{M} = \frac{1}{N} \sum_{i} M_i$$

$$X_k = \sum_{n=0}^{N-1} x_n \cdot e^{-\frac{i2\pi}{N}kn} \longrightarrow \frac{\sum_{i=1}^n A_i B_i}{\sqrt{\sum_{i=1}^n A_i^2} \sqrt{\sum_{i=1}^n B_i^2}}$$

L2H

L2\_RQSTS:DEMAND\_DATA\_RD\_HIT

#### L2M

ix86arch::LLC\_REFERENCES

L2\_LINES\_OUT:DEMAND\_CLEAN

L2\_RQSTS::ALL\_DEMAND\_MISS

L2\_RQSTS::DEMAND\_DATA\_RD\_MISS

LONGEST\_LAT\_CACHE:REFERENCE

MEM\_LOAD\_UOPS\_RETIRED:L2\_MISS

perf::LLC-LOADS

OFFCORE\_RESPONSE\_0:DMND\_DATA\_RD:ANY\_RESPONSE

#### L3H

MEM\_LOAD\_UOPS\_L3\_HIT\_RETIRED:XSNP\_NONE

MEM\_LOAD\_UOPS\_LLC\_HIT\_RETIRED:XSNP\_NONE

MEM\_LOAD\_UOPS\_RETIRED:L3\_HIT

OFFCORE\_RESPONSE\_0:DMND\_DATA\_RD:L3\_HIT:SNP\_ANY

#### L3M

ix86arch::LLC\_MISSES

#### Summary

- Hardware is complex

- ... and gets more complex with every generation

- CIT: PAPI effort that aims to alleviate complexity by

- Categorizing, Validating, and Understanding native events

- CIT deploys micro-benchmarks and data analytics