# Roadmap for the Development of a Linear Algebra Library for Exascale Computing

**SLATE: Software for Linear Algebra Targeting Exascale**

Ahmad Abdelfattah Hartwig Anzt Aurelien Bouteiller Anthony Danalis Jack Dongarra Mark Gates Azzam Haidar Jakub Kurzak Piotr Luszczek Stanimire Tomov Stephen Wood Panruo Wu Ichitaro Yamazaki Asim YarKhan

Innovative Computing Laboratory

April 4, 2018

This research was supported by the Exascale Computing Project (17-SC-20-SC), a collaborative effort of two U.S. Department of Energy organizations (Office of Science and the National Nuclear Security Administration) responsible for the planning and preparation of a capable exascale ecosystem, including software, applications, hardware, advanced system engineering and early testbed platforms, in support of the nation's exascale computing imperative.

The authors would like to thank Shane Story, Konstantin Arthurov, Murat Guney, and Sarah Knepper from the Intel MKL team for sharing their insights about the inner workings of MKL.

The authors would like to thank Clint Whaley, the author of ATLAS, for sharing his insights into the inner workings of ATLAS.

| Revision | Notes             |

|----------|-------------------|

| 06-2017  | first publication |

| 01-2018  | new cover         |

| 04-2018  | copy editing      |

# Contents

| 1 | Pref       | ace                         | 1           |

|---|------------|-----------------------------|-------------|

| 2 | 2.1<br>2.2 | Results                     | 2<br>2<br>8 |

| 3 | Hard       | ware Technology Trends      | 0           |

|   | 3.1        |                             | 0           |

|   | 3.2        |                             | 11          |

|   |            | 3.2.1 GPUs                  | 11          |

|   |            | 3.2.2 Xeon Phi              | 2           |

|   |            | 3.2.3 POWER                 | 3           |

|   |            |                             | 3           |

|   | 3.3        | Communication               | 14          |

|   |            | 3.3.1 NVLINK                | Ι4          |

|   |            | 3.3.2 InfiniBand            | 14          |

|   |            | 3.3.3 OmniPath              | 15          |

|   | 3.4        |                             | 15          |

|   |            | 3.4.1 High Bandwidth Memory | 15          |

|   |            | 3.4.2 Hybrid Memory Cube    | 6           |

|   | 3.5        |                             | 17          |

| 4 | C (:       | T                           | _           |

| 4 |            | 6,                          | 9           |

|   | 4.1        |                             | 9           |

|   |            |                             | 9           |

|   |            | -1 -                        | 6           |

|   |            |                             | 3           |

|   |            |                             | 17          |

|   | 4.2        |                             | 3           |

|   |            |                             | 3           |

|   |            |                             | 57          |

|   |            |                             | 51          |

|   |            |                             | 2           |

|   |            | 4.2.5 RATA 6                | ĸ           |

|   | 4.3                             | Consequences for SLATE                                                                              | 72                         |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------|

| 5 | Mat<br>5.1<br>5.2<br>5.3<br>5.4 | trix Layout Considerations ATLAS Layouts  MKL Packed GEMM  GPU Batched GEMM  Consequences for SLATE | 74<br>74<br>76<br>77<br>78 |

| 6 |                                 | ·                                                                                                   | 80                         |

| U | _                               | orithmic Considerations                                                                             |                            |

|   | 6.1                             | LU                                                                                                  | 80                         |

|   | 6.2                             | LDLT                                                                                                | 82                         |

|   | 6.3                             | QR/LQ                                                                                               | 83                         |

|   | 6.4                             | Mixed Precision                                                                                     | 83                         |

|   |                                 | 6.4.1 Linear Systems                                                                                | 84                         |

|   |                                 | 6.4.2 Other Algorithms                                                                              | 84                         |

|   | 6.5                             | Matrix Inversion                                                                                    | 86                         |

|   | 6.6                             | Eigenvalues and SVD                                                                                 | 86                         |

|   |                                 | 6.6.1 Singular Value Decomposition                                                                  | 87                         |

|   |                                 | 6.6.2 Symmetric Eigenvalue Problem                                                                  | 88                         |

|   |                                 | 6.6.3 Nonsymmetric Eigenvalue Problem                                                               | 89                         |

|   | 6.7                             | Consequences for SLATE                                                                              | 89                         |

| 7 | Con                             | nclusions                                                                                           | 91                         |

# List of Figures

| 2.1  | Do you call linear algebra directly?                             |       | <br>   |   |   |       |   | 3   |

|------|------------------------------------------------------------------|-------|--------|---|---|-------|---|-----|

| 2.2  | To what extent do you rely on linear algebra?                    |       | <br>   |   |   |       |   | 3   |

| 2.3  | What linear algebra routines are you using?                      |       | <br>   |   |   |       |   | 4   |

| 2.4  | Which precisions are you using?                                  |       | <br>   |   |   |       |   | 4   |

| 2.5  | What arithmetic are you using?                                   |       | <br>   |   |   |       |   | 4   |

| 2.6  | Are you interested in extended precision?                        |       | <br>   |   |   |       |   | 5   |

| 2.7  | Are you interested in lower precision?                           |       | <br>   |   |   |       |   | 5   |

| 2.8  | What is the structure of your matrices?                          |       |        |   |   |       |   | 5   |

| 2.9  | What are the properties of your matrices?                        |       |        |   |   |       |   | 6   |

|      | What is the shape of your matrices?                              |       |        |   |   |       |   | 6   |

|      | Are you solving a large number of small problems?                |       |        |   |   |       |   | 6   |

|      | 2 What is your hardware target?                                  |       |        |   |   |       |   | 7   |

| 2.13 | B Which API do you need?                                         |       | <br>   |   |   |       |   | 7   |

| 2 1  | TELD LINE M. I.S.                                                |       |        |   |   |       |   | 1.0 |

| 3.1  | High Bandwidth Memory architecture                               |       |        |   |   |       |   |     |

| 3.2  | Hybrid Memory Cube architecture                                  | <br>• | <br>٠. | ٠ | • | <br>• | • | 16  |

| 4.1  | Basic divide and conquer summation algorithm                     |       |        |   |   |       |   | 30  |

| 4.2  | Task-recursive divide and conquer summation algorithm            |       |        |   |   |       |   | 30  |

| 4.3  | Offloading the task-recursive divide and conquer algorithm       |       |        |   |   |       |   | 31  |

| 4.4  | Serial implementation of a Mandelbrot set generation algorithm   |       |        |   |   |       |   | 32  |

| 4.5  | Parallel implementation of a Mandelbrot set generation algorithm |       |        |   |   |       |   | 33  |

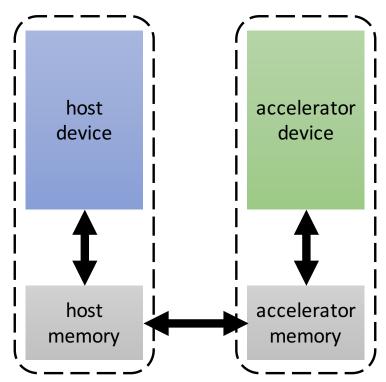

| 4.6  | OpenACC abstract accelerator model                               |       |        |   |   |       |   | 36  |

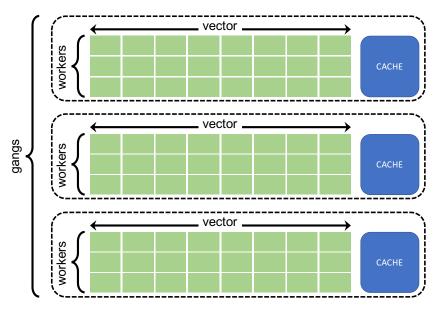

| 4.7  | OpenACC levels of parallelism                                    |       |        |   |   |       |   | 37  |

| 4.8  | A sample Jacobi iteration                                        |       |        |   |   |       |   | 38  |

| 4.9  | An example for the kernels directive                             |       |        |   |   |       |   | 39  |

| 4.10 | An example for the combined parallel loop directive              |       |        |   |   |       |   | 39  |

|      | Jacobi iteration using the parallel loop directive               |       |        |   |   |       |   | 40  |

| 4.12 | 2 Jacobi iteration using the kernels directive                   |       | <br>   |   |   |       |   | 41  |

|      | An example of a data region enclosing two parallel loops         |       |        |   |   |       |   | 42  |

|      | An example code that uses data clauses with array information.   |       |        |   |   |       |   | 43  |

| 4.15 | Improving data locality for a parallelized Jacobi iteration      |       | <br>   |   |   |       |   | 43  |

|      | An example of unstructured data scopes                           |       |        |   |   |       |   | 44  |

|      | 7 An example of the update directive.                            |       |        |   |   |       |   | 45  |

|      |                                                                  |       |        |   |   |       |   |     |

| Asynchronous operations in OpenACC                                 | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OpenACC interoperability using host_data regions                   | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OpenACC interoperability using device_ptr data clause              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

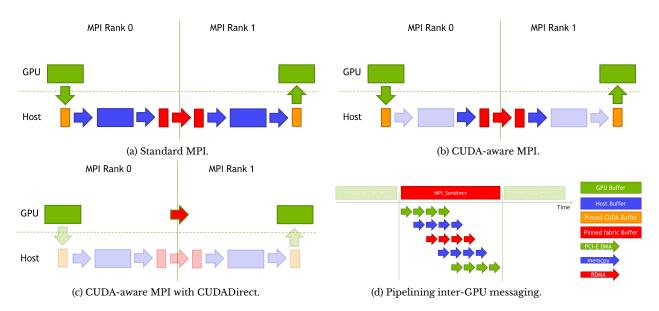

| Illustration of GPUDirect                                          | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Inter-node communication with CUDA-aware MPI                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

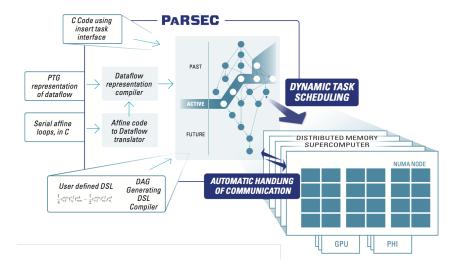

| The PaRSEC framework                                               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Classic Cholesky factorization using loops and basic kernels.      | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PaRSEC Cholesky factorization based on JDF                         | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PaRSEC Cholesky factorization using Sequential Task Flow.          | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A Circuit Simulator in Legion pseudo code                          | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A Conjugate Gradient linear solver in Legion.                      | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

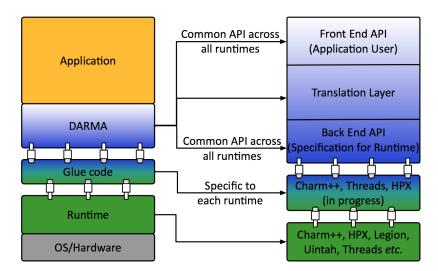

| The structure of DARMA.                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| An example of DARMA code                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Example of the AccessHandleCollection construct                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Declaration of a multidimensional array in Kokkos.                 | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Different mapping of the data layout for a CPU and a GPU in Kokkos | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Atomic exchange for arbitary data types in Kokkos                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Two-level parallel inner product in Kokkos                         | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A RAJA equivalent to a simple loop in C++                          | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Different encapsulations in RAJA.                                  | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

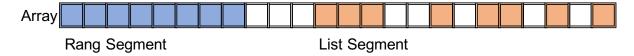

| IndexSet segments in RAJA                                          | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

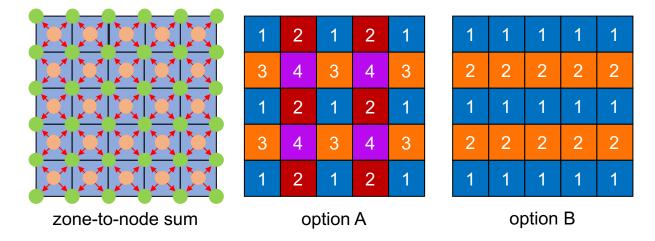

| Zone-to-node sum with two loop ordering options in RAJA            | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

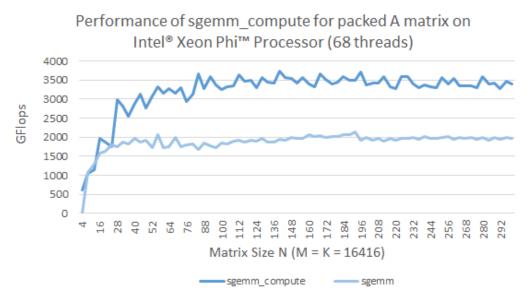

| Performance of sgemm_compute() on Xeon Phi                         | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

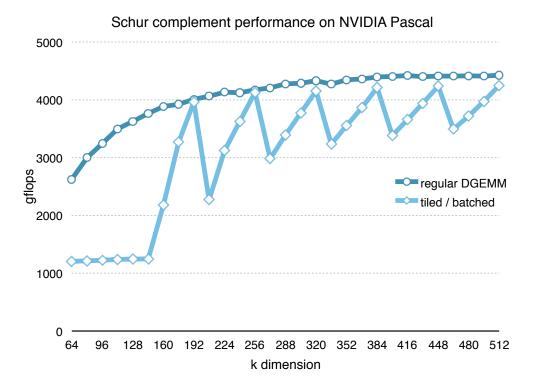

| Performance of Schur complement on NVIDIA Pascal                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                    | OpenACC interoperability using host_data regions. OpenACC interoperability using device_ptr data clause. Illustration of GPUDirect Inter-node communication with CUDA-aware MPI The PaRSEC framework. Classic Cholesky factorization using loops and basic kernels. PaRSEC Cholesky factorization based on JDF. PaRSEC Cholesky factorization using Sequential Task Flow. A Circuit Simulator in Legion pseudo code. A Conjugate Gradient linear solver in Legion. The structure of DARMA. An example of DARMA code. Example of the AccessHandleCollection construct. Declaration of a multidimensional array in Kokkos. Different mapping of the data layout for a CPU and a GPU in Kokkos. Atomic exchange for arbitary data types in Kokkos. Two-level parallel inner product in Kokkos A RAJA equivalent to a simple loop in C++. Different encapsulations in RAJA. IndexSet segments in RAJA. Zone-to-node sum with two loop ordering options in RAJA. Performance of sgemm_compute() on Xeon Phi. |

# List of Tables

| 3.1 | Comparison of Memory Technologies.         | 1       |

|-----|--------------------------------------------|---------|

| 4.1 | Most significant OpenACC features.         | 3       |

| 4.2 | Comparison of OpenACC and OpenMP standards | $3^{4}$ |

| 4.3 | OpenACC data clauses.                      | 49      |

## **CHAPTER 1**

## **Preface**

The Scalable Linear Algebra PACKage (ScaLAPACK) was released 22 years ago in 1995. To put that into perspective, this was one year after MPI standard version 1.0 was released, and two years before the OpenMP Fortran 1.0 specification was released. The fastest machine on the TOP500 list was the Japanese Numerical Wind Tunnel, with peak performance of 235.8 gigaFLOP/s. This was also the year Microsoft acquired the Mosaic from the National Center for Supercomputing Applications to build Internet Explorer.

The past two decades witnessed tectonic shifts in hardware technology followed by paradigm shifts in software technology, as well as a plethora of algorithmic innovations in scientific computing. However, no viable replacement for ScaLAPACK that would channel this technological progress into a robust software package emerged. The Software for Linear Algebra Targeting Exascale (SLATE) is meant to be its replacement, and the objective of this document is to provide an overview of the cutting-edge solutions required to accomplish that mission.

# **CHAPTER 2**

# **ECP Applications Survey**

In February 2017, the SLATE team circulated a survey to the Exascale Computing Project (ECP) applications teams to asses their needs for dense linear algebra functionality. Forty responses were collected—twenty-five from the project's PIs and co-PIs and fifteen from other team members. Here, the responses to the most important questions are summarized.

## 2.1 Results

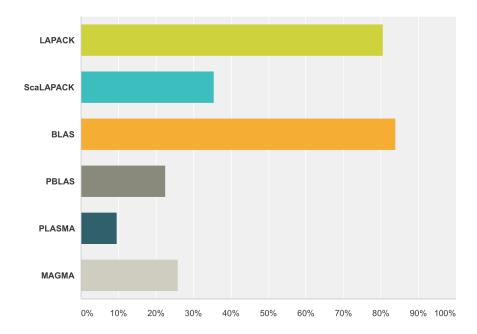

LAPACK 25 ScaLAPACK 11 BLAS 26 PBLAS 7 PLASMA 3 MAGMA 8

Figure 2.1: Is your application directly calling any of the following packages? Mark all that apply.

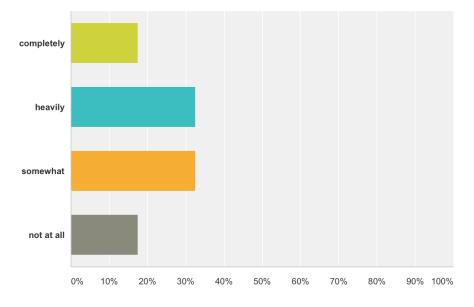

completely 7 heavily 13 somewhat 13 not at all 7

Figure 2.2: To what extent does your application rely on dense or band linear algebra operations?

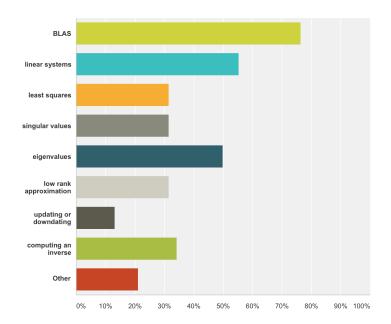

29 **BLAS** linear systems 21 least squares 12 singular values 12 19 eigenvalues low rank approximation 12 updating or downdating 5 computing an inverse 13 Other 8

18

32

Figure 2.3: What linear algebra routines are you using? Mark all that apply.

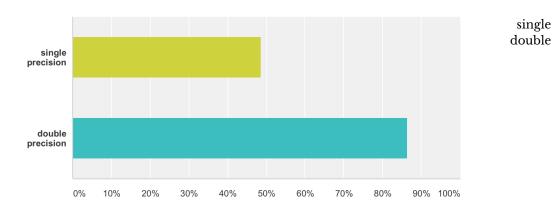

Figure 2.4: Which precisions are you using? Mark both if applicable.

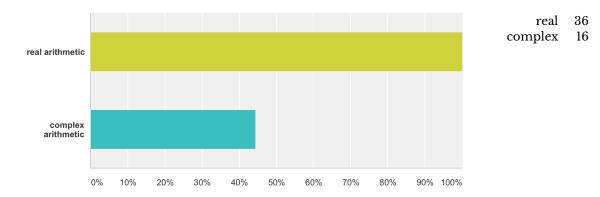

Figure 2.5: What arithmetic are you using? Mark both if applicable.

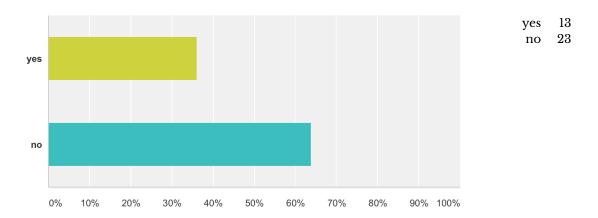

Figure 2.6: Are you interested in extended precision, e.g., double-double or triple-float?

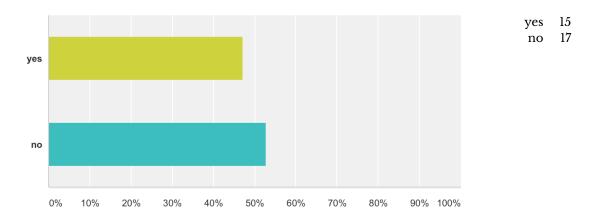

Figure 2.7: Are you interested in lower precision, e.g., half precision (16-bit floating point).

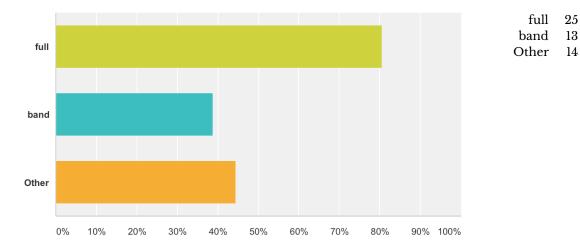

Figure 2.8: What is the structure of your matrices? Mark all that apply.

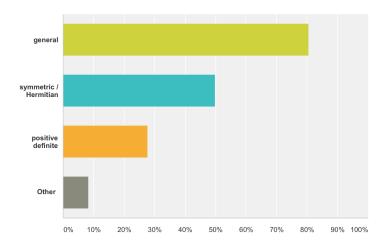

general 26 symmetric / Hermitian 16 positive definite 8 Other 3

Figure 2.9: What are the properties of your matrices? Mark all that apply.

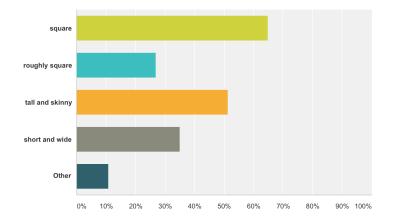

square 21 roughly square 10 tall and skinny 16 short and wide 13 Other 4

Figure 2.10: What is the typical shape of your matrices? Mark all that apply.

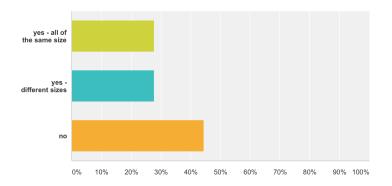

yes - all of the same size 10 yes - different sizes 7 no 14

Figure 2.11: Are you solving a large number of small independent problems? (matrices smaller than 500x500)?

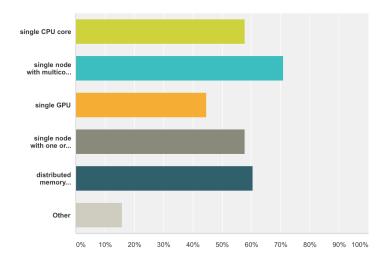

single core 19

single node multicore 23

single GPU 15

single node +GPUs 18

dist. mem. [+GPUs] 22

Other 6

Figure 2.12: You need dense linear algebra routines for what target? Mark all that apply.

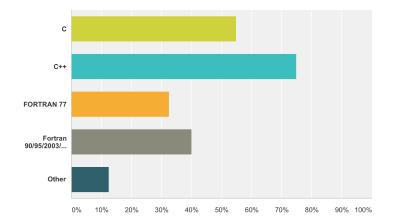

C 19 C++ 26 FORTRAN 77 11 Fortran 90/95/2003/... 14 Other 4

Figure 2.13: Which API do you need? Mark all that apply.

## 2.2 Consequences for SLATE

This summary is based on the results of the survey as well as follow-up interaction with the applications teams. Here we summarize the main observations.

Impact: Dense linear algebra is ubiquitous in Department of Energy (DOE) ECP applications. 80% of respondents indicated reliance on Linear Algebra PACKage (LAPACK) and basic linear algebra subprograms (BLAS), 35% reliance on ScaLAPACK, and 20% reliance on parallel basic linear algebra subprograms (PBLAS). The newer libraries, Parallel Linear Algebra for Scalable Multi-core Architectures (PLASMA) and Matrix Algebra on GPU and Multicore Architectures (MAGMA), have much smaller traction. While some have adopted MAGMA, the adoption of PLASMA is minimal. Half of the respondents indicated that their applications rely completely or heavily on dense or band linear algebra operations. Only 20% of respondents indicated no need for such operations at all.

While traditional DOE applications—relying heavily on partial differential equation (PDE) solvers (fusion, combustion, wind turbines, stellar explosions)—use little dense linear algebra and mostly indirectly, there are a number of applications in quantum mechanics, computational chemistry, particle physics, and material science that rely heavily on dense linear algebra software (QMCPACK, NWChemEx, General Atomic and Molecular Electronic Structure System [GAMESS], Exascale Atomistic capability for Accuracy, Length and Time [EXAALT]). Naturally, dense linear algebra routines are used heavily by sparse direct solvers, e.g., FBSS (STRUMPACK).

Types of Problems: The needs of the ECP applications basically span the coverage of BLAS and LAPACK. 75% of respondents indicated the need for BLAS, 50% indicated the need for linear solvers and eigenvalue solvers, and 30% indicated the need for least squares solvers, singular value solvers, low-rank approximations, and constructing an inverse of a matrix. There is also some need for updating and downdating capabilities.

80% of respondents deal with full matrices and 40% of respondents deal with band matrices. At the same time, 80% of respondents deal with general (non-symmetric) matrices, 40% deal with symmetric matrices, and 30% deal with symmetric positive definite matrices. Also, while in most cases the matrices are square (60%), there is also a strong need for operations on matrices that are tall and skinny, and on matrices that are short and wide (50% and 35% respectively). This, again, confirms the need for supporting the fairly wide range of matrix shapes and properties—close to the coverage of BLAS and LAPACK.

Target Hardware: There seems to be a universal agreement that all types of architectures should be supported, including homogeneous multi-core systems as well as heterogeneous, accelerated systems, and support for multiple accelerators per node is desired. There also seems to be a universal agreement that distributed memory capabilities are a must, although we only heard a single request for actual exascale capabilities. The NWChemEx team expressed interest in dense solvers capable of dealing with O(1M) matrices.

Arithmetic and Precision: The majority of applications require double precision, while about half also use single precision. All need real arithmetic, while about half needs complex arithmetic. About a third indicated interest in extended precision (double-double or triple-float), while almost half indicated interest in lower precision, e.g., 16-bit half precision. This is a clear indicator that there is a strong need for providing flexibility going beyond the four basic precisions supported by LAPACK, ScaLAPACK, PLASMA, and MAGMA.

**Desired APIs:** Basically, APIs for all common HPC programming languages are needed: C, C++, legacy Fortran, and modern flavors of Fortran. At the same time, there is significant interest in C++ interfaces. 75% of respondents indicated the need for a C++ API.

**Batched Operations:** There is a significant demand for batched dense linear algebra operations, i.e., operations on large numbers of small matrices. The two cases—one where all the matrices in the

batch are of the same size and the other where the batch contains matrices of different sizes—seem to be equally important. Obviously, this is a node-level capability.

In summary, the SLATE software needs to:

- serve as a replacement for BLAS/PBLAS and LAPACK/ScaLAPACK,

- support distributed memory systems with accelerators,

- provide a C++ API in addition to traditional APIs,

- facilitate the use of other precisions beyond the traditional set of four.

Further, the results indicate that the project should:

- standardize the C++ APIs of BLAS and LAPACK,

- standardize the API for batched BLAS and LAPACK operations.

## **CHAPTER 3**

## Hardware Technology Trends

## 3.1 Upcoming Machines

The Collaboration of Oak Ridge, Argonne, and Livermore (CORAL) is a joint procurement activity among three of the US Department of Energy's (DOE) National Laboratories. It was launched in 2014 to build state-of-the-art high-performance computing technologies that are essential for supporting U.S. national nuclear security and are key tools used for technological advancement and scientific discovery [61]. The Argonne Leadership Computing Facility (ALCF) will contract with Intel and Cray to build "pre-exascale" systems, while Lawrence Livermore National Laboratory (LLNL) and the Oak Ridge Leadership Computing Facility (OLCF) will contract with IBM. This configuration of systems will enable explorations of architecture diversity along the path to exascale computing [63, 69].

The ALCF CORAL system, named Aurora, is built on the foundation of Intel's HPC scalable system framework. Aurora is designed to provide peak performance of 180 petaFLOP/s from >50,000 nodes while consuming 13 MW of power [69]. Argonne and Intel have also provided an interim system, called Theta, which is enabling ALCF users to transition their applications to the new technology [63, 68].

The LLNL CORAL system, named Sierra, aims to provide a 120–150 petaFLOP/s peak. The Sierra system will include (1) compute nodes: POWER Architecture Processor, NVIDIA Volta, NVMe-compatible PCIe 800 GB SSD, greater than 512 GB DDR4 + HBM (high bandwidth memory), and coherent shared memory, (2) compute racks: standard 19-inch with warm-water cooling, and (3) the compute system: 2.1–2.7 PB memory, 120–150 petaFLOP/s, and 10 MW. The Global Parallel File System will have 120 PB usable storage and 1.0 TB/s bandwidth [78].

The OLCF CORAL system, named Summit, is planned to deliver more than five times the computational performance of OLCF's Titan's 18,688 nodes using only approximately 3,400 nodes. Each Summit node will contain multiple IBM POWER9 CPUs and NVIDIA Volta GPUs all connected via NVIDIA's high-speed NVLink and a huge amount of memory. Each node will have over half a terabyte of coherent memory (HBM + DDR4) addressable by all CPUs and GPUs—plus an additional 800 gigabytes of NVRAM [39].

## 3.2 Processing

## 3.2.1 **GPUs**

Graphical Processing Units adopt a many-core architecture. GPUs typically pack thousands of very lightweight processing cores rather than tens of large, powerful cores (as in modern multi-core CPUs and the Xeon Phi architecture). Generally, a GPU thread executes slower than a CPU thread. However, their slow single-thread execution is compensated by their ability to execute orders of magnitude more concurrent threads than modern CPUs. Therefore, GPUs usually outperform CPUs in executing kernels that include large amounts of parallelism, and where throughput matters more than latency.

Since the Fermi product line, GPU compute cards have always consisted of tens of streaming multiprocessors (SMs). Each SM consists of single-precision CUDA cores, double-precision units, texture units, warp schedulers, special function units, and fast memory levels (register file, shared memory, and sometimes a constant read-only memory). Through the Fermi, Kepler, and Maxwell architectures, the number of SMs was relatively low (typically 8–15), and the main memory was an off-chip graphics double data rate (GDDR) memory. The Pascal architecture [1] brought some drastic changes to these two aspects. First, a Pascal GPU packs 56–60 SMs, but the number of cores per SM is relatively low (e.g., 192 cores in Kepler vs. 64 cores in Pascal). In addition, the main memory is now a stacked memory architecture (High Bandwidth Memory [HBM2]) that brings substantial improvement in memory bandwidth (e.g., ~250 GB/s for Kepler vs. 720 GB/s for Pascal). Over the generations, several other features have been added, such as atomic operations, dynamic parallelism, Hyper-Q, warp shuffle instructions, and improved power efficiency.

The latest commercially available GPU adopts a Pascal architecture [1]. A Pascal GPU (P100) offers several architectural enhancements, summarized below:

- 1. Improved performance: the P100 GPU is capable of delivering up to 5.3/10.6 teraFLOP/s of performance. For double precision, this is a more than  $4\times$  improvement over the last FP64-capable GPU (Kepler).

- 2. Half-precision arithmetic: The Pascal P100 GPU is the first NVIDIA GPU to support half-precision arithmetic, with up to 21.2 teraFLOP/s. This new floating-point standard is particularly important for deep learning and AI applications.

- 3. High Bandwidth Memory (HBM2): the P100 chip incorporates a stacked memory architecture, with up to 720 GB/s bandwidth. Unlike the previous generations, this is the first NVIDIA GPU to support error-correcting code (ECC) on the hardware level. Previous generations enable a software ECC, which consumes about 12–15% of the available memory bandwidth on average.

- 4. NVLink: a new high-speed interconnect that can deliver at least  $5\times$  the speed of the PCIe interconnect.

- 5. The P100 GPU is the first to support FP64 atomic operations on the hardware level.

- 6. Compute preemption at an instruction level granularity, rather than a thread block granularity in the previous generations.

- 7. A 2× improvement in the remote direct memory access (RDMA) bandwidth, which is fundamentally important for multi-GPU configurations.

The anticipated Volta GPU brings even more performance and power efficiency than the P100 GPU. While a detailed description of the V100 architecture is yet to come, these are the features announced for the upcoming GPU [2]:

- 1. Improved performance: the Tesla V100 GPU is at least 1.4× faster than the P100 GPU in many computational workloads and benchmarks. This includes matrix multiplication (FP32 and FP64), fast Fourier transform (FFT), and the STREAM benchmark.

- 2. Faster interconnect: the Volta NVLink delivers up to 300 GB/s, which is almost twice as fast as the bandwidth of the Pascal NVLink.

- 3. A new instruction set architecture (ISA) with double the number of warp schedulers as Pascal. The Volta GPU incorporates a larger and faster unified L1 cache/shared memory. Unlike Pascal, which has a separate 64KB shared memory and a slower 24KB L1 cache, the V100 GPU has a unified 128KB L1 cache/shared memory. The L1 cache is, therefore, as fast as shared memory. The latter is also configurable up to 96KB. The V100 GPU also has 6MB of L2 cache (against 4MB on the P100 GPU).

- 4. Independent thread scheduling: All previous GPUs had a single program counter (PC) and stack for a warp of 32 threads. As per the Volta GPU, each thread has its own PC and stack. It also supports a new synchronization mechanism among divergent threads in the same warp.

- 5. As a result of the independent thread scheduling, the volta GPU, along with CUDA 9.0, deprecates the previous shuffle and compares intrinsics, and replaces them with other intrinsics that synchronize across a warp.

- 6. Tensor acceleration: the V100 GPU brings eight tensor cores per multiprocessor. These cores perform mixed-precision matrix math (FP16/FP32) with significant speedups compared to the P100 GPU. With up to 120 teraFLOP/s, the tensor cores are of particular importance for deep learning applications.

- 7. The Volta GPU comes with CUDA 9.0, bringing new functionality such as cooperative thread groups, synchronization across thread blocks, and the elimination of implicit warp synchronization.

## 3.2.2 Xeon Phi

Knights Landing (KNL) is the codename for the second generation of Intel's Xeon Phi many integrated core (MIC) architecture. The Theta system is a pre-exascale machine being installed and put into early production at Argonne National Lab by the ALCF. Theta utilizes Intel's Knights Landing along with the Cray Aries interconnect via the XC40 supercomputer architecture. The ALCF Theta XC40 system achieves a nearly 10 petaFLOP/s peak with 2,624 nodes. Theta contains the 64-core 7230 KNL variant. The 7230 KNL chip has 64 cores that are organized into 32 tiles, with 2 cores per tile, connected by a mesh network and with 16 GB of in-package multichannel DRAM (MCDRAM) memory. The core is based on the 64-bit "Silvermont" Atom Core (1.40 gigahertz [GHz]) which has 6 independent out-of-order pipelines, two of which perform floating-point operations [68].

The 7230 and 7250 KNL variants utilize 14 nanometer (nm) lithography—similar to the "Broadwell" Xeon E5 and E7 server processors—to achieve 3.05 teraFLOP/s peak double-precision. The 68 cores on the 7250 KNL chip are also based on the "Silvermont" microarchitecture and support four execution threads. Both the 7230 and 7250 KNL variants have two AVX-512 vector processing units per core. The cores are tiled in pairs that share 1MB of Level 2 (L2) memory. The tiles of both variants are linked using a 2-D mesh interconnect that also connects to the 384 GB DDR4-2400 memory (115.2 GB/s) through two controllers. The cores are also connected to 16GB of MCDRAM, providing up to 490 GB/s of sustained bandwidth through the 2-D mesh interconnect. The memory bandwidth per KNL core is approximately 11 GB/s for small thread counts, while its predecessor the Knights Corner only provided 3.6 GB/s [54].

Knights Hill (KNH) is the codename for the third generation of Intel's Xeon Phi MIC architecture. Little has been publicly announced about the Knight's Hill processor beyond the plan to manufacture it with a 10 nm lithography process (SC 14) [69]. ALCF's Aurora, a supercomputer capable of 180-petaFLOP/s

planned to be built for Argonne National Lab in 2018, was originally announced as utilizing KNH processors as part of the CORAL joint procurement activity [63]. The US Department of Energy fiscal year 2018 budget request is not specific regarding the Aurora supercomputer [62].

#### **3.2.3 POWER**

The Summit is OLCF's next flagship supercomputer. It will consist of 3,400 nodes, each featuring 2 IBM POWER9 CPUs and 6 NVIDIA Volta GPUs connected by NVLink and 512GB high bandwidth memory addressable by both CPUs and GPUs and 800GB of NVRAM.

For developers transitioning to Summit, OLCF provides the Summitdev workshop with node architectures one generation earlier than Summit—the 2 IBM POWER8 CPUs with NVLink and 4 NVIDIA Tesla P100 GPUs. The IBM POWER8 [74] is a reduced instruction set computer (RISC) microprocessor from IBM built using IBM's 22-nm technology. Compared to previous generation IBM POWER7 processors, the POWER8 processor is an improvement both in single-thread performance and in the number of cores. The IBM POWER8 processor features up to 12 cores per socket, 8 threads per core, as well as 32 KB instruction cache, 64 KB L1 data cache, 512 KB L2 cache, and 8 MB L3 cache per core. Each core can issue up to ten instructions per cycle, and complete eight instructions per cycle. As for its functional units, the POWER8 has two independent fixed-point units (FXU), two independent load-store units (LSU) plus two more load units, and two independent floating-point vector/scalar units (VSU). The maximum double-precision floating-point issue rate is four floating multiply add instructions (fmadds) per cycle; the maximum single-precision rate is 8 fmadds per cycle. The single instruction, multiple data (SIMD) width is two for double precision and four for single precision. Thus, the peak double-precision performance is Freq × 8 × #cores. For a 3.5 GHz frequency, 20-core node, the peak double-precision performance is 560 gigaFLOP/s.

The upcoming IBM POWER9 CPUs [72] will be built using 14-nm Fin Field-effect transistor (FinFET) technology. It will come in four variants with either (1) two sockets optimized (scale-out [SO]) or multiple sockets optimized (scale-up, [SU]) configurations, (2) 24 simultaneous multi-threading 4 cores (SMT4), or 12 SMT8 cores. Compared to a POWER8 chip with the same SMT, frequency, and core count configuration, the POWER9 socket achieves  $1.5 \times$  floating-point performance,  $2.25 \times$  graph analytics performance, and something between  $1.5 \times$  and  $2.25 \times$  for commercial, integer, scripting, and business intelligence workloads [79]. For HPC workloads, POWER9 is also a powerful acceleration platform equipped with NVLink 2.0 and various high-bandwidth low-latency interconnects (PCIe G4, Coherent Accelerator Processor Interface [CAPI] 2.0, and New CAPI) to connect to accelerators such as application-specific integrated circuits (ASICs) and field-programmable gate arrays (FPGAs).

## 3.2.4 ARM

Recently, many ARM vendors have been trying to introduce server-class ARM chips to challenge Intel's Xeon in datacenter servers as Japan, China, and Europe seem to be interested in an ARM-based exascale supercomputer. Products in the server-class ARM processors include Cavium with its high core count ThunderX and ThunderX2 lines. The current production chips, ThunderX, features up to 48 cores per socket in a two-socket configuration using 28-nm process technology, clocked at up to 2.5 GHz (though 2.0 GHz is most prevalent). The next generation ThunderX2 promises 2–3× improvement in performance and will be etched using a 14-nm FinFET process. Architectural changes from ThunderX to ThunderX2 probably include larger caches, out-of-order pipelines, and more cores (56) per socket, clocked at 3.0 GHz. ThunderX2 is also purported to be much more power efficient than ThunderX in addition to having twice the high bandwidth memory.

To cater to the HPC market, the ARMv8-A architecture was extended with vector instructions. This was announced by ARM at the HotChips'16 conference [76]. The specifics of the Scalable Vector Extension

(SVE) were later specified in more detail [77]. The SVE significantly enhances the vector processing capabilities of AArch64 execution in the ARM architecture in a flexible way—unmodified binary code can efficiently run on future CPUs with longer vector lengths (128-2048 bits in 128-bit increments). This is called the Vector Length Agnostic programming model. Compared to previous media processingfocused SIMD instructions (e.g., the ARM NEON, or ARMv7 Advanced SIMD), the SVE introduces scalable vector lengths, gather load and scatter store, per-lane predication, and some other features to make it a better compiler target and allow increased parallelism extraction for HPC workloads. One particularly interesting property in SVE is its vector length agnostic, which increases its future proofness. Traditionally, SIMD is incorporated into an ISA whenever the vector length is increased. We have seen this in x86 ISA with a handful of extensions: MMX, 3DNow!, SSE, SSE2, SSE3, SSE3, SSE4, AVX, AVx2, AVX512). The SVE, conversely, does not have to be revised every time the vector length is increased. In addition, portability across different microarchitectures is improved with CPUs featuring different vector lengths with different tradeoffs among cost, power, area, and performance. Moreover, SVE has many other advanced vector-processing functions that make vectorization more applicable and efficient. As a result, SVE can achieve better speedups than NEON, even with the same vector lengths for many applications and notably dense linear algebra. It also allows CPU designers to find their optimum vector lengths depending on individual objectives and constraints. The SVE will be supported by lead partners of ARM such as Fujistu for its Post-K supercomputer. It is unclear whether Cavium's ThunderX2 will support SVE.

## 3.3 Communication

## **3.3.1 NVLINK**

NVLink is an HBM technology developed by NVIDIA in response to the slow communication via the PCIe interconnect. Current PCIe technology (Gen. 3.0, 16 lanes) has a theoretical peak bandwidth of 16 GB/s. With a significant portion of the computing power being delivered by the coprocessor, communication via this port quickly becomes the bottleneck when running distributed codes on a GPU-accelerated cluster. NVIDIA's NVLink-enabled P100 GPUs feature four NVLink connections, each providing a peak bandwidth of 20 GB/s per direction. The NVLink technology can be used in different configurations as well. Connecting all NVLink lanes to the CPU augments the host-accelerator bandwidth by another 80 GB/s per direction, which gives the GP100 in total 160 GB/s of bidirectional bandwidth. Alternatively, a peer-to-peer configuration uses some of the lanes to improve the GPU-to-GPU communication. NVLink also boasts up to 94% bandwidth efficiency.

Aside from the massive bandwidth of NVLink, it is also designed to enable the clustering of GPUs and CPUs for them to appear as a single computing unit. NVLink enables this abstraction by supporting load/store semantics [40], which allow programmers to directly read/write peer GPUs' local memory and the CPU's host memory all in a common shared memory address space. Furthermore, remote atomic memory operations are supported on peer GPUs for fast synchronizations. With the unified memory space in CUDA 8 and page-faulting hardware in the GP100 GPU, NVLink thus pushes forward something like a Symmetric Multiprocessing (SMP) capability for CPUs to GPU accelerators (and to CPUs that support NVLink). In fact, the NVIDIA's DGX-1 server clusters two CPUs with eight P100 GPUs, with the GPU↔CPU links being PCIe and the GPU↔GPU link being NVLink.

## 3.3.2 InfiniBand

InfiniBand originated in 1999 from the merger of two competing technologies: Future input/output (I/O) and Next Generation I/O. Companies participating in the initial development included: Compaq, Dell, HP, IBM, Intel, Microsoft, and Sun. The first specification of the architecture was released in 2000.

The vision was that InfiniBand would replace PIC for the I/O and Ethernet for the interconnect. This plan was disrupted by the burst of the dot-com bubble. Mellanox shipped the first 10 Gbit/s devices in 2001.

Currently, InfiniBand is the most commonly used interconnect for supercomputers. InfiniBand adapters and switches are made by Mellanox and Intel, and Oracle is also entering the market with its own hardware. The important feature from an HPC standpoint is that InfiniBand provides RDMA capabilities for low CPU overhead. The current technology, InfiniBand EDR, provides around 24 Gbit/s of theoretical effective throughput per link ( $1\times$ ). Links can be aggregated, and most systems use a  $4\times$  aggregate for the total theoretical effective throughput of close to 100 Gbit/s.

## 3.3.3 Omni-Path

Omni-Path is an interconnection technology from Intel developed to address scaling weaknesses currently impeding HPC. From a commercial standpoint, its main competition is InfiniBand. Omni-Path has its roots in two acquisitions: acquisition of the InfiniBand technology from QLogic, and acquisition of the Aries interconnect technology from Cray. As a result, Omni-Path combines the QLogic True Scale architecture and its associated software stack with high performance features of Cray's Aires. Notably, it is compliant with the Open Fabrics Alliance (OFA) stack for RDMA fabrics.

The current generation of Omni-Path products delivers 100 Gbit/s of bandwidth per port and port-to-port latencies comparable to InfiniBand EDR. Notably, Intel already ships Xeon Phi processors with integrated Omni-Path fabric. Intel also differentiates the technology from other RDMA fabrics by pointing to a set of unique features, including traffic management and robust error detection, e.g.:

Adaptive Routing — monitors the network and selects the least congested path to rebalance the load. While this is not a unique solution, Intel points out advantages of its implementation, which are based on cooperation between the fabric manager and the switch ASICs.

**Dispersive Routing** — distributes traffic across multiple paths instead of sending all packets from source to destination via a single path. This promotes efficiency through redundancy, as well as better load balancing.

**Traffic Flow Optimization** — breaks up variable length packets into fixed size-containers for transmitting over the link. At the same time, higher priority containers can be inserted into the stream of lower priority containers, which allows the reduction of latency variation high-priority traffic experiences in the presence of low-priority traffic.

## 3.4 Memory

## 3.4.1 High Bandwidth Memory

During the last few years, memory interfaces have been undergoing major changes, and a number of new technologies are becoming available in HPC architectures. The basic technologies in previous generation's memory interface (DDR4) were defined in 2008, and even though there have been power and performance updates, these changes have been incremental. The maximum bandwidth for 64-bit DDR4 is approximately 26 GB/s, which is be insufficient for many applications on highly multi-core architectures.

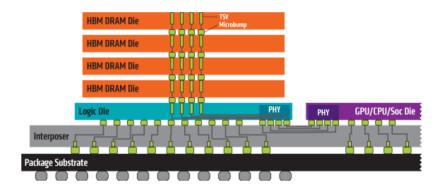

HBM is a memory interface promoted by AMD, NVIDIA, and Hynix. HBM is a new type of memory architecture with low power consumption and ultra-wide communication lanes. It uses vertically-stacked

memory chips interconnected by microscopic wires called through-silicon vias (TSVs) (Figure 3.1).

Figure 3.1: High Bandwidth Memory architecture (source: http://www.amd.com/en-us/innovations/software-technologies/hbm).

HBM's primary purpose is for use in graphics cards, and it is designed to serve as a replacement for GDDR5, which is the current graphics memory interface standard. The HBM interface is intended to decrease power consumption, enable more dense circuitry for the higher bandwidth required today, and to allow the memory interface to be attached off-chip rather than requiring on-chip integration.

HBM can achieve a bandwidth of 100+ GB/s per memory stack, whereas GDDR5 only got up to 28 GB/s per chip. In terms of energy consumption, HBM is a substantial improvement when measured in bandwidth/watt compared to GDDR5. HBM achieves 35+ GB/s of bandwidth per watt, whereas GDDR5 achieves 10.66 GB/s of bandwidth per watt. The newer HBM-2 standard can achieve even better bandwidth and power efficiency.

## 3.4.2 Hybrid Memory Cube

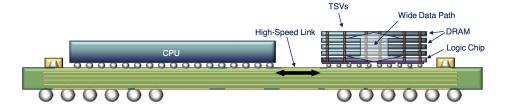

The Hybrid Memory Cube (HMC) interface is managed by a consortium, the participants of which include Altera (Intel), ARM, IBM, Micron Technology, Open-Silicon, Samsung, SK Hynix, and Xilinx, along with a large number of adopters.

HMC architecture consists of stacked memory chips that are bonded together using TSVs in conjunction with a high-speed logic layer (Figure 3.2).

Figure 3.2: Hybrid Memory Cube architecture (source: http://wccftech.com/micron-hybrid-memory-cube-3-0-specification/).

One of the goals of HMC is to remove the duplicated control logic of modern memory systems, simplify the design, and connect the entire stack in a 3-D configuration—all using a single control logic layer to handle the memory management. The logic layer in HMC controls all aspects of the memory, and

the host memory control is simplified to handle requests and responses. The HMC logic layer provides error detection and management capabilities, atomic operations, reliability and availability features, and scale-out device-chaining capabilities.

| Memory        | HMC Gen3                                      | HBM-2                                         |

|---------------|-----------------------------------------------|-----------------------------------------------|

| Size          | 8 GB                                          | 8 GB                                          |

| Max Bandwidth | 480 GB/s                                      | 256 GB/s                                      |

| Expandable    | Yes, chain modules                            | No                                            |

| Power         | Higher                                        | Lower                                         |

| Target        | HPC, networking                               | Graphics, networking, small form-factors      |

| Benefits      | High bandwidth; scalability; power efficiency | High bandwidth; scalability; power efficiency |

| Cost          | High                                          | Medium                                        |

Table 3.1: Comparison of Memory Technologies.

A single HMC module can provide more than  $15 \times$  the performance of a DDR3 module, utilizing 70 percent less energy per bit than DDR3 DRAM technologies, and is contained in 90 percent less space.

The (HMC) design has a higher power consumption than the HBM design, but achieves a higher bandwidth. Putting the entire control logic into the HMC allows modules to be chained together to increase capacity.

## 3.5 Consequences for SLATE

The hardware technology trends, described in this chapter, have significant consequences for dense linear algebra in general and the SLATE project in particular. Here we summarize the most impactful developments:

Large Numbers of Cores: The number of CPU cores per node is going to be large. Presently, a single Xeon Phi is already at the level of 72 cores; one ThunderX ARMv8 system is at the level of 96 cores. As this trend continues, we will likely have hundreds of cores per node by the time we reach exascale. However, it is still the rule of thumb that the best performance can be extracted from ScaLAPACK by running one process per core. It should be clear now that this is a completely unsustainable direction for any numerical software. While message-passing is the paradigm of choice for the foreseeable future, node-level parallelism has to be addressed with some form of multithreading.

Omnipotent GPUs: GPUs are here to stay, and GPU-accelerated machines will have virtually all of their performance on the GPU side. A single node of the Summit supercomputer is expected to have 40 teraFLOP/s of GPU performance. Further, it is likely to have about 1 teraFLOP/s of CPU performance. This means that only 2.5% of raw performance comes from CPUs. A gap of such magnitude requires a fundamentally different approach to designing numerical software, as the process can no longer be framed in terms of "offloading" work to GPUs. Instead, new packages have to be built from the ground up with a GPU-centric mindset.

Starved Communication: Communication is getting worse. Consider the following: The Titan supercomputer has node bandwidth of 6.4 GB/s and node peak performance of around 1.4 gigaFLOP/s, while the Summit supercomputer is advertised at 23 GB/s of node bandwidth and 40 teraFLOP/s of node peak performance [5]. So, while the bandwidth increases about 3.6 times, the node peak

performance increases more than 28 times, which means that the communication to computation ratio is about 8 times worse (basically one order of magnitude). This makes bandwidth a very scarce resource. While various techniques can be used to deal with the latency, little can be done about the lack of bandwidth. This means that SLATE will have to be very conservative in its use of bandwidth, stay away from any techniques of dynamically rebalancing work, and rely on statically partitioning matrices among distributed memory nodes. Dynamic scheduling is only applicable at the node level.

Complex Node Memories: SLATE will have to deal with two-fold memory complexity. First, a GPU-accelerated node is basically a globally-addressable distributed memory system. In terms of programmability, memory traffic can be handled by a software coherency protocol. This does not change the fact that data transfers will have to be carefully orchestrated for good performance. Second, the introduction of 3-D-stacked memories creates an extra level of memory on the CPU side, with cache-like appearances, but no hardware cache coherency protocol. While low-level memory management may not be within the scope of SLATE, SLATE needs to utilize data layout that does not handicap memory motion to and from GPUs, or between traditional RAM and 3-D memory. Specifically, the ScaLAPACK matrix layout may need to be retired as it is not particularly friendly to transfers through memory hierarchies.

In summary, the SLATE software needs to:

- expose work in large chunks to be able to saturate large numbers of CPU cores and/or multiple GPU devices per node,

- be extremely conservative it its use of network bandwidth, refrain from dynamic work migration between nodes, and

- offer an alternative to the traditional matrix layout that will streamline memory management and messaging.

## **CHAPTER 4**

## Software Technology Trends

The U.S. DOE has identified performance portability as a priority design constraint for pre-exascale as well as upcoming exascale systems [3, 4]. The development of parallel software that is portable across architectures can be provided through the use of standard APIs, e.g., OpenMP, OpenACC, and the Message Passing Interface (MPI); standardized language features like co-arrays and DO CONCURRENT from the Fortran standard [70]; or new parallelization features [52] proposed for inclusion in the C++17 standard, etc. However, because the standardizations and efficiently implementing them for high-performance are very slow processes, many of these features remain inadequate for performance portability, especially in terms of accelerator programming with heterogeneous compute capabilities and deep memory hierarchies. To address this, various programming environments and frameworks have been developed on top of standards as well, e.g., PaRSEC, Legion, Distributed Asynchronous Resilient Models and Applications (DARMA), Kokkos, and RAJA. Still, performance portability remains a major challenge. Therefore, it is necessary to understand, explore, and assess the current standards—as well as environments—in order to select the best programming models and practices to maximize performance portability, productivity, sustainability, and to balance their trade-offs for the development of the SLATE linear algebra library for exascale computing.

## 4.1 Standards

## 4.1.1 C++

Historically speaking, ScaLAPACK, PBLAS, and BLACS have been written in a combination of FORTRAN 77 and C (ANSI and K&R versions). The complexities of modern hardware and software systems for HPC necessitated contemporary programming languages to ease the development process and shift the burden of common development tasks onto the software stack and the accompanying tool chain.

A quickly-increasing set of scientific applications relies on a mix of programming languages; thus, linking multiple language runtimes has become a commonplace. C++ has become a prevalent implementation

language for large scientific software collections such as Trilinos, and, as a consequence, is an indispensable part of large and scalable applications that are of great importance to the national defense and energy agendas.

As a somewhat arbitrary boundary, we choose to focus here on the transition from C+03 to C++11. The former was mostly a bug-fix release of the C++98 standard that addressed a large number of defect reports. The latter, on the other hand, slipped a largely aspirational deadline in the 2010s and ultimately landed almost a decade after the standard preceding it.

Even today, C++11 is not universally implemented by all compilers. The prominent examples are vendor compilers that often substantially lag behind in features. Namely, IBM's XLC tool chain is notoriously conservative, and NVIDIA's compiler (from CUDA 8 as of this writing) still misses some features to make it C++11-complete. These are among the targeted compilers—we must therefore to take this situation into consideration.

A defensive strategy that selects a C++ feature set to be used throughout SLATE should be developed. To that end, we might consider a two-compiler strategy whereby both performance and programmer productivity are addressed. Ideally, as the project progresses, support for modern features will grow such that workarounds can be replaced with more legitimate solutions.

In the following subsections we describe the modern C++ features most relevant to the development of SLATE.

## Overloading